如何选择正确的芯片互连方式?

2018-05-12 11:16:48 来源:麦姆斯咨询 评论:0 点击:

据麦姆斯咨询报道,芯片制造商在更高性能、更低功率和更快上市时间等方面竞相追逐,封装方式的选择也随之变得越来越丰富。

五花八门的选择令人眼花缭乱,导致在可加快产品上市时间、降低先进封装成本方面花费的努力化为乌有。

其中芯片互连的选择是最让人抓狂的工作。目前可选择的范围有:有机、硅、玻璃中介层(interposer),从多层布线去连接不同芯片的桥接(bridge)。同时还有各种各样的扇出(fan-out)方法,可达到与中介层和bridge同样的高性能与低功耗。

推动这些活动的因素是:尺寸缩小的成本和性能优势正在减少。虽然这种影响在模拟电路方向已存在一段时间了,但由于芯片设计的应用还不成熟,目前已开始对专用集成电路(ASIC)产生影响。

在人工智能、深度学习和机器学习这些代表了芯片热门市场的领域,其训练算法几乎是在不断变化的。关于如何分配处理云端、边缘器件与中间层服务器间的决策也是如此。这使得在先进节点上构建ASIC变得更加困难,因为当它进入市场时,它可能已经过时了。

汽车行业的情况基本相同,许多技术仍处于转型阶段。在如医疗电子、增强现实与虚拟现实、物联网(IoT)与工业物联网(IIoT)等蓬勃发展的市场中,没有人确切地知道架构将会是怎样的,或是这些共性最终将会怎样。与过去不同的是,当芯片制造商在移动电话、个人电脑和服务器socket展开竞争时,新兴市场和终端市场的应用也正在分裂。

促使先进封装进入主流市场主要有以下巨大好处:

• 使用如硅通孔(TSV)、bridge和键合金属层等宽度更宽的通道代替细细的连线来传输信号,可显著改善性能。

• 通过将不同芯片放置在彼此更近的位置代替使用相同的芯片,以减少发送信号所需的能量以及移动数据所需时间,从而缩小关键元器件之间的距离。

• 在模拟IP的情况下,由于模拟电路无法从缩小尺寸特性中获益,元器件可混合搭配多个工艺节点,这就能够节省大量的时间。

尽管如此,先进封装还是会增加其复杂性。封装领域有太多选择,目前还不清楚哪种方法会胜出。其结果很大程度上取决于互连的选择,而互连则是不同芯片间的“粘合剂”。

eSilicon公司业务与企业发展部门的副总裁Patrick Soheili说:“我们业务成长的关键在于缩短开发周期,特别是在人工智能领域。一方面,不甘落后,当前又买不起芯片。另一方面,也担心这些芯片是否经得住时间的考验。而我们的目标就是将两者兼顾。”

美国国防高级研究计划局(Defense Advanced Research Projects Agency,简称DARPA)一直在推动chiplets作为一种标准化组装元器件的方法。这是由美满电子科技(Marvell Semiconductor,简称Marvell)利用其MoChi架构开发的首个商业化模块化方法。Marvell仍在公司内部使用自己的芯片,并可根据客户需要定制模块。DARPA的CHIPS项目有了新进展:允许来自多家公司的chiplets进行混合和匹配,并通过中介层进行组合。

Soheili补充道:“chiplets已确定是解决方案的一部分。但实现起来并不容易。如果7nm的ASIC必须放置在中间,且连接到180nm的chiplets上,那么就必须有一个可以排列并通过链接发送数据的器件。”

不同类型的中介层

使用先进封装的企业发现,这种技术既耗时又昂贵。通常情况下认为,一旦各类方法能够标准化,该工艺就能变得更快更经济。这可能涉及到规避使用硅中介层(silicon interposer),因为在需要多块掩膜版的复杂器件中,仅中介层自身的价格就高达100美元。

Brewer Science公司业务发展部总监Ram Trichur说:“总的来说,硅中介层是昂贵的。因此,问题就是能用什么来替代它。有机中介层(organic interposer)的挑战一直未解决。目前很多公司都在应对这些挑战,并为有机中介层提供特定的方式而努力着。有些情况下可直接安装,另一些情况则需要基板。”

京瓷(Kyocera)、新光(Shinko Electronics)和三星(Samsung)各自独立开发了使用标准环氧树脂薄膜制造工艺的有机中介层。其中关键问题在于将热膨胀系数(CTE)与硅的相匹配。当然,这并不是硅中介层的问题,但却一直是无法解决有机层压板与底部填充不足的原因。根据几篇相关主题的技术论文的发现,减薄中介层的厚度目前对解决该问题有很大帮助。

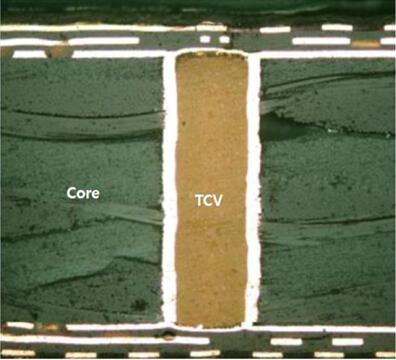

图1:有机中介层(来源:NVIDIA / SEMCO)

不过,目前尚不清楚这是否会成为一种商业上替代硅中介层的可行方法。Fraunhofer EAS的研究工程师Andy Heinig说:“有了有机中介层,你就能得到与硅中介层相同的连线和连线间的距离,这种情况下,最终解决所有问题的成本基本与之前的成本相同。但问题是,需要系统级研究来找出设计的最佳解决方案。其中可以改变的因素就是,在这些器件上需要传输的大量数据。如果可以把数据量降低到某个数值,就可以使用有机中介层。因此找到这个数值,要比使用硅互连更有意义。”

其实,有机中介层并不是唯一的选择。Brewer的Trichur说:“可调玻璃中介层也可使用。玻璃的CTE与硅相匹配,损耗低,因此适用于高频应用。玻璃也适用于板级(panel-level)工艺,且成本很低。”

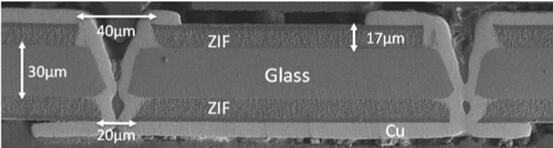

图2:测试样品的玻璃中介层(来源:乔治亚理工大学)

中介层的替代选择

2.5D硅中介层或2.1D有机中介层最吸引人的一点是,可以利用TSV阵列代替细连线来提高产量。这就实现了多通道与堆栈型动态随机存取存储器(DRAM)的连接,即所谓的高带宽内存(high-bandwidth memory)。

目前,在2016年推出的HBM 2 JEDEC标准中,通过类似Hybrid Memory Cube的可选内存控制器可支持多达8颗DRAM芯片堆栈。HBM 2支持高达2 GT/s的传输速率,每个封装体的带宽可达256 GB/s。在未来几年中,HBM 3将会使带宽增加一倍,达到512 GB/s。目前也有关于HBM 3+和HBM 4的讨论,尽管还不清楚确切的速度和时间进度。

所有器件的目标都是:耗电更低,在处理器和存储器之间更快更多地传输数据,同时2.5/2.1D并不是目前唯一的实现方法。许多业内人士表示,一些新器件正在Fan-out封装中开发使用铜柱(堆栈式逻辑电路、存储器、逻辑电路)。台积电(TSMC)已具备集成扇出型(Integrated Fan-Out,InFO)封装技术的供货能力。

其他先进Fan-out使用了不同的方法。日月光(Advanced Semiconductor Engineering,ASE)工程高级主管John Hunt说:“Fan-out取代了中介层的位置。Chip-last更接近于无机中介层,且使用4层金属层,其良率目前已高达99%。中介层真正目的是增加有源器件的间距,这样就能布线HBM2。先进Fan-out会表现出更好的热性能和电性能,是因为铜的重新布线层(RDL)更厚,通孔(via)电阻更小。但它们只适用于无需1μm连线的情况。”

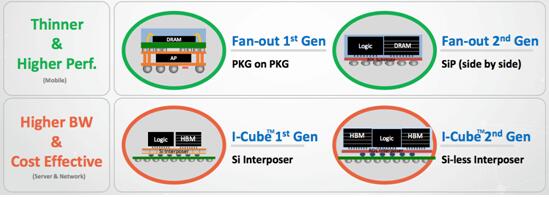

Fan-out技术也有很多选择:chip first、chip last、die up、die down。也有倒装芯片(flip-chip)、系统级封装(system-in-package)和衬底上的扇出(fan-out on substrate)。

重要的是,解决这个问题的方法有很多,目前已可通过多种封装方式实现高速互连。几年前的封装方式主要有:fan-out、扇入(fan-in)、2.5D与3D集成电路以及多芯片模块,这些封装方式均有显著的性能和成本差异。目前,这些方法都有了更多选择,且选项的数量还在不断增加,从而模糊了彼此之间的界限。

桥接(Bridge)

另一种方法是使用低成本的桥接(bridge)。英特尔(Intel)拥有“嵌入式多芯片互连桥”(EMIB)技术,该技术为英特尔的代工厂客户提供了连接多个布线层的选择。

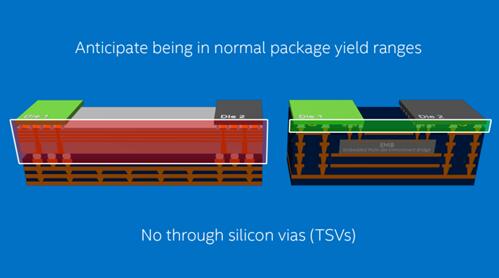

图3:英特尔的EMIB技术(来源:英特尔)

与此同时,三星(Samsung)也宣布为其客户提供RDLbridge,RDLbridge与RDL的作用完全相同。

图4:三星的互连选择方案(来源:三星)

这两种方法均可降低先进封装的成本,但它们比中介层的限制更多。因此,bridge虽然可以提供两个或更多芯片之间的高速连接,但使用这种方法对可连接逻辑电路的HBM堆栈数量是有限制的。

此外,虽然bridge本身的价格要比那些填充硅通孔的中介层要便宜,但由于这种互连是平面的,因此可能会更具挑战性。同样,影响多芯片封装的翘曲问题在bridge技术中也存在。

未来的目标和问题

这种封装体内部和封装体之间的互连技术近期得到了如此多的关注,其中一个原因就是需要处理的数据量正在显著增加。其中一些数据必须使用多处理器或多核在本地处理,另一些数据则需要在中间服务器或云端远程处理。所有计算模型均需大量的数据吞吐,且将如此大规模的吞吐量构建到7/5nm的芯片中会变得更加困难。

根据以往的经验法则,在芯片上处理速度总会比在芯片外更快。但是,在同一封装体中,两芯片间的距离要比信号通过从SoC的一端到另一端的布线要短得多,但在先进节点上则可能遇到RC延迟。这些实现起来都不简单,无论如何,在5G等新领域还会变得更糟。

Brewer的Trichur说:“目前材料和工艺面临多种挑战。首先,就是结构性封装问题。其次,当进入5G时代时,会发现集成电介质材料的空隙问题。5G将面临下一个材料挑战。因此现在需要将所有新材料和新工艺都集成在小型封装中。这将存在更多的改变,因此必须利用新工艺和新材料集成天线。这就是全新的挑战。”

另一个先进封装可以发挥关键作用的市场是人工智能、机器学习和深度学习领域。这里的关键指标是性能和功耗,另外更大的挑战是能够快速推出新设计。其中的问题是,训练算法几乎处于不断变化的状态,因此增添新型处理器或IP的时效性是很重要的。如果处理器或内存架构需要每6个月更换一次,那么18个月的开发周期就根本跟不上节奏。

如果试图利用现成的元器件来解决单芯片的问题,可能会导致一系列集成器件自身的问题。ArterisIP公司的营销副总裁Kurt Shuler说:“大型SoCs中的问题是,企业正试图将所有东西集成在一起,但IP模型却处于不同的抽象级别和速度。这就要求处理好互连模型,能够使其正常工作。即便如此,正是由于模型的‘血统’不同,例如起初建模并非为pin或TCM(紧密耦合内存)接口而开发,或者建模的精准级别不同:cycle-accurate、approximately timed(AT)或loosely timed(LT)。因此我们看到的产品并非大规模发展而来的。它们只是从一个问题点发展出来。”

先进封装可以帮助解决这个问题,并达到一定效果。但到目前为止,大多数先进封装更多的是为特定的应用和特定的项目服务,而没有开发出能让多数公司均可使用的平台。

Achronix公司系统工程副总裁Raymond Nijssen说:“如果它运行良好,就能完成伟大的任务。但这条路仍有很多岔路:采用不同中介层的解决方案或者干脆取消中介层。同时还存在不同的数据速率,因此目前有一些具有极高数据速率的解决方案。做什么样的chiplets,取决于做chiplets的原因。是因为封装中有很多焊球而太过昂贵?还是因电力供给上限所导致的功效问题?”

结论

到目前为止,这些问题都没有明确的答案。但好消息是,目前有很多选择,且其中许多解决方案已经通过了市场的验证。

下一个挑战将是在封装世界中建立规模效益。这将要求该行业缩小其选择范围。到目前为止,许多封装方法的实施成本都很高,这就是它们会出现在智能手机等各个领域的原因,因为只有在那里才有足够的规模来抵消开发成本,其实在网络芯片领域价格也不成问题。

未来,先进封装将变得几乎无处不在,以推动人工智能、机器学习和深度学习推断(inference)在边缘节点、汽车和其他各类新兴市场广泛应用。这就要求在设计上具有一定程度的灵活性,相当于大规模定制。这是封装世界最终的走向,但还需一些更难的选择来实现这一目标。互连将仍是所有决定的核心,但使用何种互连还有待实践的检验。

延伸阅读:

《先进基板技术及市场现状-2018版:嵌入式芯片和互联、基板式PCB趋势》

推荐培训:

2018年7月13日至7月15日,麦姆斯咨询主办的“MEMS制造工艺培训课程”将在无锡举行,培训内容包含:(1)硅基MEMS制造工艺(体微加工技术、表面微加工技术和CMOS MEMS技术);(2)MEMS特殊薄膜工艺技术(AlN和PZT等压电薄膜的沉积工艺);(3)掩膜版制造工艺;(4)非硅基MEMS制造工艺(LIGA、准LIGA、精密机械加工、微注塑等);(5)半导体激光器VCSEL制造工艺;(6)选修课程:MEMS设计工具Tanner软件及应用(MEMS设计-建模与仿真方法、MEMS代工厂合作成功案例)。

麦姆斯咨询

联系人:彭琳

电话:17368357393

E-mail:penglin@memsconsulting.com