扇出型封装面临哪些光刻技术的挑战?

2019-02-17 14:45:44 来源:麦姆斯咨询 评论:0 点击:

据麦姆斯咨询报道,先进封装技术已进入大量移动应用市场,但亟需更高端的设备和更低成本的工艺制程。

更高密度的扇出型封装正朝着具有更精细布线层的复杂结构发展,所有这些都需要更强大的光刻设备和其它制造设备。

最新的高密度扇出型封装技术正在突破1µm线宽/间距(line/space)限制,这被认为是行业中的里程碑。拥有这些关键尺寸(critical dimension,CD),扇出型技术将提供更好的性能,但是要达到并突破1µm的壁垒,还面临着制造和成本的挑战。此外,目前还只有少数客户需要这样先进的封装技术。

尽管如此,扇出型封装在众多市场上正变得越来越受欢迎。“移动设备仍然是低密度和高密度扇出型封装的主要增长驱动力。”日月光(ASE)高级工程总监John Hunt表示,“随着我们一级和二级的扇出技术获得认证,汽车行业将开始加速发展。高端市场的服务器应用也在增长。”

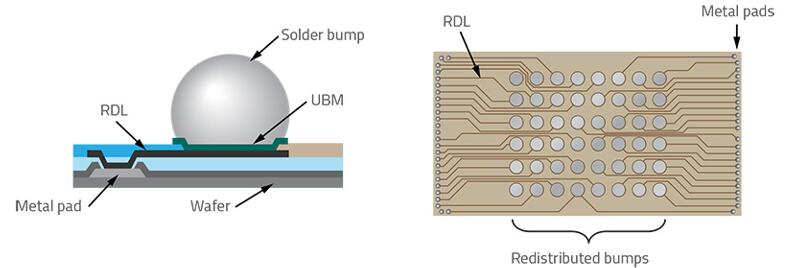

重布线层(Redistribution Layer,RDL)是扇出型封装的关键部分。RDL是在晶圆表面沉积金属层和介质层并形成相应的金属布线图形,来对芯片的I/O端口进行重新布局,将其布置到新的、节距占位可更为宽松的区域。RDL采用线宽(line)和间距(space)来度量,线宽和间距分别是指金属布线的宽度和它们之间的距离。

图1:重布线层

扇出型技术可分成两类:低密度和高密度。低密度扇出型封装由大于8μm的line/space(8-8μm)的RDL组成。高密度扇出型封装有多层RDL,CD在8-8μm及以下,主要应用于服务器和智能手机。一般来说,5-5μm是主流的高密度技术,1-1μm及以下目前还在研发中。

“就设计规则的激进程度而言,目前仍然有各种各样的扇出型技术。很多产品都受到外形尺寸、性能以及成本等因素的影响。”Veeco全球光刻应用副总裁Warren Flack说道,“具有较小CD的重布线层能够减少扇出型封装中的重布线层数。这能降低整体封装成本并提高良率。”

成本是许多封装厂需要考虑的因素。因为并非所有客户都需要高密度扇出型封装。挑战性(非常小)CD的扇出技术相对昂贵,仅限于高端客户。好消息是,除了高密度扇出型封装之外,还有其它大量低成本的封装技术可供选择。

然后,另一方面,客户也正在推动封装厂商降低其制造成本,特别是对于扇出型封装和其它先进封装。在扇出型封装中,有几个工艺步骤,包括光刻——一种在结构上形成细微特征图案的方法。

在封装领域,有几种不同的光刻设备类型,例如对准式曝光机、直接成像、激光烧蚀和步进式曝光机(stepper),每项技术能力不同。换言之,封装厂商可能会使用不同的设备类型进行扇出型封装。

什么是扇出型封装?

扇出型封装技术在封装市场是较为热门的话题。在扇出型技术中,裸片直接在晶圆上封装。由于扇出型技术并不需要中介层(interposer),因此比2.5D/3D封装器件更廉价。

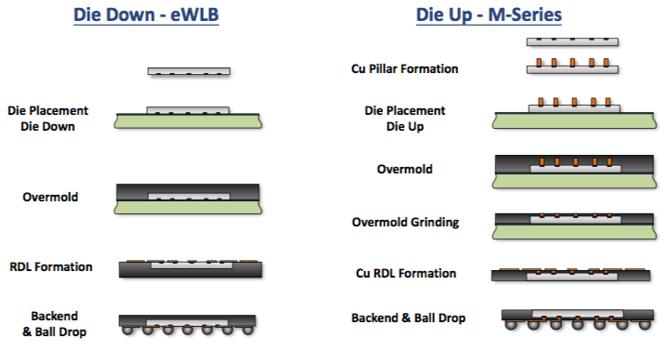

扇出型技术主要可以分作三种类型:芯片先装/面朝下(chip-first/face-down)、芯片先装/面朝上(chip-first/face-up)和芯片后装(chip-last,有时候也被称为RDL first)。

在chip-first/face-down工艺流程中,晶圆厂首先在晶圆上加工芯片,然后将晶圆移至封装厂进行芯片切割。最后,通过芯片贴装系统,再将芯片放置在临时载板上。

EMC(epoxy mold compound,环氧模塑料)被塑封在芯片和载板上,形成所谓的重构晶圆(reconstituted wafer)。然后,在圆形重构晶圆内形成RDL。

在RDL制造流程中,先在衬底上沉积一层铜种子层,再在该结构上涂布一层光刻胶,然后利用光刻设备将其图案化。最后,电镀系统将铜金属化层沉积其中,形成最终的RDL。

RDL的CD取决于应用。许多扇出型封装不需要先进RDL。在可预见的未来,5-5µm及以上的封装仍将是主流技术。在高端领域,ASE正朝着1-1μm及以下的RDL进军。与此同时,台积电(TSMC)也紧跟步伐,目前正在研发0.8μm和0.4μm的扇出型技术。先进扇出型技术终将支持高带宽存储器(high-bandwidth memory,HBM)的封装。

“扇出型方法有很多种。我们可以看到CD越来越小,越来越有挑战性。铜柱的间距也越来越小。”Veeco的光刻系统亚洲业务部门总经理Y.C. Wong说道,“通常,主流的RDL仍在5-5μm及以上。目前我们可以看到也有2-2μm或3-3μm在生产。而现在1-1μm还只是处于研发状态。当5G真正发展起来以及随着存储器带宽需求变高时,以上需求都将被驱动。这也将推动市场对2-2μm和3-3μm及以下的更多需求。”

尽管如此,所有扇出型技术仍然都面临着挑战。“扇出型封装的主要挑战是翘曲(warpage)/晶圆弯曲(wafer bow)问题。此外,芯片放置也会影响晶圆的平整度和芯片应力。所以芯片偏移(die shift)给光刻步骤和对准带来了挑战。”Yole分析师Amandine Pizzagalli说道。

成本也是关键因素之一。具有挑战性CD的封装往往更昂贵。相反,CD要求低的封装则更便宜。在任何情况下,客户对IC封装的价格都是敏感的。他们希望尽可能降低封装成本。因此,他们希望封装厂商降低制造成本。

这个故事还有另外一面。封装客户可能想要一款具有挑战性RDL的扇出型产品。但是该封装技术必须达到一定的需求量才具有研发的可能性。如果封装需求量达不到目标,则很难获得回报。因此,目前来说可能还没有动力驱动更小RDL的封装研究。

对准曝光机(Aligners)vs. 步进式曝光机(steppers)

当然,光刻技术在扇出型和其它封装类型中起着关键作用。在晶圆厂,光刻设备被用于纳米级的特征图案,这也是至关重要的。同时,在封装厂,光刻和其它设备被用来处理凸点(bump)、铜柱(copper pillar)、RDL和硅通孔(TSV),这些结构都属于微米级。

根据Yole的数据表明,2019年用于封装的光刻设备市场规模预计将达到1.416亿美元,高于2018年的1.287亿美元。Pizzagalli称,所有的新设备采购清单中,约85%涉及步进式曝光机,其次是掩模对准曝光机,占比相比前者低15%。

掩模对准曝光机和步进式曝光机都属于光刻类别。为此,该工艺从光掩模版开始。设计人员设计IC或封装,然后将其转换成文件格式,再基于该格式开发光掩模版。

光掩模版根据给定图形进行设计。掩模版显影后,被运送到晶圆厂或封装厂。将掩模版放置在光刻设备中。该设备发射光线透过掩模版,在器件上形成图案。

多年来,掩模对准曝光机一直是封装界的主流光刻设备。“掩模对准曝光机的工作原理是将掩膜版的全区域图形投影到衬底上。由于投影光学器件没有减少,掩模版必须放置在晶圆附近。因此,其分辨率被限制在约3μm line/space。”EV Group业务发展总监Thomas Uhrmann表示。

如今,掩模对准曝光机主要用于封装、MEMS和LED(发光二极管)领域。“虽然在生产过程中很难达到3µm以下的line/space要求,但在先进封装中,掩模对准曝光机还有其它优势。例如,掩模对准曝光机在需要高强度和高曝光次数的凸点和厚抗蚀剂曝光领域具有性能和成本优势。”Uhrmann说道。

然而,对于更先进的应用,封装厂则会转向使用一种称为步进式曝光机的光刻系统。使用先进的投影光学系统,步进式曝光机的分辨率高于掩模对准曝光机。

步进式曝光机可以将图像特征以更小比例从掩模版转移到晶圆上。不断重复该过程,直到晶圆被加工完成。封装领域步进式曝光机的主要参与者有Canon(佳能)、Rudolph(鲁道夫)、Veeco(维易科)及其它竞争者。

对于许多应用来说,封装厂商选择使用步进式曝光机出于几个原因。“当我们开始研究步进式曝光机可以做些什么的时候,我们就可以提供一些显著的改进。”Veeco公司的Flack说道,“缩小CD在过去几年里一直是我们考虑的重要因素。步进式曝光机也正在缩小套刻精度以匹配CD。现在,它必须能够处理更多不同尺寸的衬底。”

与此同时,在晶圆厂,芯片制造商使用193nm波长的光刻系统来进行特征成像。然而在封装厂,由于特征尺寸更大,封装厂无法使用此波长的设备。相反,他们使用的光刻机波长更长,如436nm(g-line)、405nm(h-line)和365nm(i-line)三种波长。

在封装过程中,一些步进式曝光机仅具备i-line波长,而有一些则支持更多的波长。例如,Veeco推出的一种称为宽波段步进式曝光机,就支持三种不同波长——436nm、405nm和365nm,通常是由宽波段光谱汞灯产生的。

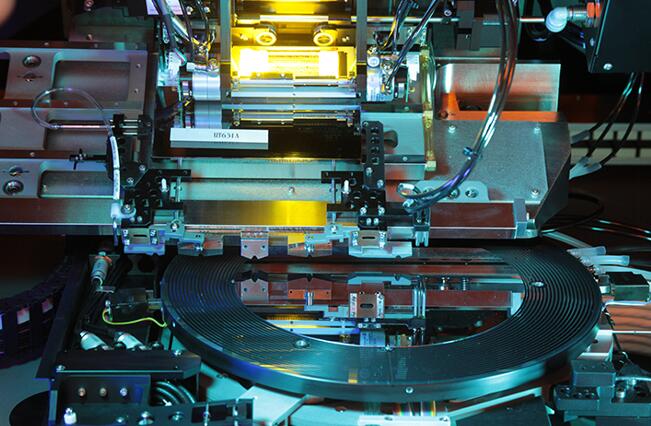

图2:Veeco步进式曝光机内部构造

对于更具挑战性的CD,该步进式曝光机可被调整为支持“仅i-line”模式,用于处理1-1μm的特征图形。此外,该设备还支持“ghi”模式,处理2-2μm及以上的应用。

步进式曝光机可用于一系列IC封装中,包括扇出型封装。在扇出型封装中,光刻设备有助于完成RDL。

这些系统还必须处理芯片偏移问题。如上文所述,当芯片嵌入重构晶圆中时,它们会随着制程发生移动,造成芯片偏移,从而影响良率。

为了解决这个问题,业界正在开发具有更好对准技术的光刻设备,以补偿芯片偏移。“有两种方法可以解决这个问题。从光刻的角度来看,你可以尽可能多地修正它、可以调整晶圆上的刻度、可以调整放大率等。但这是假设所有芯片都以同样的方式移动的情况下。如果偏移是随机的,那么几乎不可能纠正这种情况。”Veeco的Flack说,“对于高端应用,我们需要努力确保芯片不会偏移。在某些情况下,可以通过放置和对准芯片的技术来实现。”

芯片偏移仍然是所有扇出技术持续存在的挑战。另一挑战是制备RDL。在5-5μm范围内通过RDL进行扇出封装几乎没有或完全没有问题。甚至在2-2μm范围内的RDL也在生产中。

随着扇出型封装不断向1-1μm及以下发展,挑战越来越大。目前能解决此问题的诀窍是以高良率制备更精细的RDL。

目前该行业已经可以达到1-1μm的分辨率。例如,Veeco在步进式曝光机中使用“仅i-line”模式,显示分辨率为1-1μm。步进式曝光机具有可变数值孔径(numerical aperture,NA)物镜和1X掩模板。

然而尽管如此,还是存在一些挑战。根据Veeco和Imec最新的论文中所述,在制备RDL过程中,必须保证铜足够厚,以降低金属线的电阻。因此,光刻胶的纵横比必须最大化。根据该论文,这需要具有较大焦深的光刻设备来处理扇出技术出现的高度变化。

同时,有些公司提供“仅i-line”系统。例如,佳能最新的i-line设备采用孔径为0.24的物镜,确保分辨率≤0.8μm。

“领先的1µm先进封装工艺需要使用化学放大原理的光刻胶,由于其光致酸产生剂的特性,仅对i-line波长敏感。因此,它需要i-line曝光光源来实现小于1µm的分辨率。”佳能的营销经理Doug Shelton说道,“要求宽波段曝光的客户将使用成熟的DNQ光刻胶来对准粗糙的图案层,这些光刻胶对i-line和h-line波长敏感,而对g-line波长不敏感。对于那些挑战性较小的应用,我们可以利用系统,该系统可以选择允许宽波段i/h-line曝光,以提高粗加工的产出量。”

因此,使用当今的技术将RDL突破1µm是有可能的,但目前尚不确定。这也是封装行业一直在争论的话题。然而,不管步进式曝光机的波长类型,突破1-1μm都存在一些挑战。光刻设备当然是有能力达到的,但目前的RDL流程还存在其它问题。

“当降到1-1μm以下时,会遇到其它与光刻无关的问题,这将限制其被采用的速度。”Veeco公司的Flack说道,“只要种子层占铜线宽度的一小部分,它就能很好地工作。当小于1μm时,种子层占线宽的比例增加,就会出现低良问题。”

简而言之,传统的RDL工艺是突破1-1μm的潜在障碍。“在这一点上的转变,将是行业面临的真正挑战。”Flack表示。

因此,该行业同时也在研究其它工艺流程,如双大马士革工艺(dual damascene)。多年来,芯片制造商一直使用双大马士革工艺来实现晶圆厂后道工艺(backend-of-the-line,BEOL)中芯片的铜互连。

在双大马士革工艺中,BEOL和封装的工艺步骤类似。在封装中,绝缘层沉积在衬底上。然后,对沟槽进行图案化和刻蚀,并用铜填充沟槽。

对于封装来说,双大马士革工艺是可行的,可以将RDL降到1-1μm及以下。“这项工艺很好,但价格昂贵。有技术解决方案,但成本效益可能不高。”Flack说。

台积电(TSMC)目前也在探索双大马士革工艺,但对大多数厂商来说,价格太昂贵了。因此,该行业还需在此“竞技场”上实现经济效益的突破。

激光成像、烧蚀等光刻技术

激光直接成像(laser direct imaging)是另一种用于封装的光刻技术。激光成像类似于直写或无掩模(maskless)光刻。它不需要直接使用掩模版就能实现在芯片上进行加工,因此削减了封装成本。

奥宝科技(Orbotech)和迪恩士(Screen)是激光直接成像系统的供应商。据消息称,另一家公司Deca也开发了具有专利的激光直写技术。

激光成像可以解决扇出型封装中的芯片偏移问题。如上所述,第一步是构建重构晶圆。然后,使用芯片贴装系统将芯片放置在晶圆上。

“问题就出现在这里。当你把芯片放在上面时,芯片彼此之间并不完美。很难将芯片精确地保持在我们想要的微米范围内。”Deca首席技术官Tim Olson表示。

Deca公司的“自适应图案化(Adaptive Patterning)”技术则是解决芯片偏移的一种方法。ASE是Deca的投资者,正在基于这种图案化技术生产M系列扇出型产品。

图3:M系列扇出型封装与传统eWLB扇出型封装的对比

Deca的技术包括四个模块的工艺流程——晶圆准备、拼板、扇出和检查。它支持研发具有更精细的RDL的5-5μm多层扇出型封装。

在晶圆准备过程中,可在芯片上电镀铜。然后,在拼板步骤中,使用高速系统以每小时28000颗芯片的速度将芯片放置在重构晶圆中。相比之下,传统的芯片贴装系统每小时只能完成2000多颗芯片。

然后,通过使用检查技术来测量晶圆上每个芯片的实际位置。Olson解释道:“芯片测量检查是拼板加工过程中的最后一步,用于制造过程中每个拼板的实时设计。”

然后,RDL以芯片先装/面朝下的流程开发。在曝光步骤期间,系统重新计算RDL图案以适应每片晶圆中的每颗芯片偏移。这个过程只需要28秒。总产出量为每小时120片晶圆。

“自适应图案化是一种系统,旨在自动补偿制造过程中的自然变量,而不是专注于消除所有变量。”Olson说道,“在典型的应用中,通过芯片贴装、注塑和其它工艺步骤,允许芯片在‘X’轴和‘Y’轴上的变量高达60μm。自适应图案化通过制造中的实时设计自动消除了97%的变量,实现了2μm以下的有效互连公差。目前我们正在开发中的下一代自适应图案化技术将支持2μm的特性,尺寸将缩小为0.8μm。”

ASE计划在2019年或2020年使用来自Deca的相同技术,提升面板级扇出型封装。同时,该封装也将使用自适应图案化技术。

与此同时,Suss MicroTec公司也在开发一种叫做激光烧蚀(laser ablation)的干法图案化工艺。Suss的准分子烧蚀步进式曝光机结合了基于掩模版的图案化烧蚀。可以实现3μm的line/space,而2-2μm也在进展中。

“准分子激光烧蚀是利用高功率紫外(UV)准分子激光源的特性直接去除材料。典型的波长是308nm、248nm和193nm。”Suss光子系统总裁兼总经理Markus Arendt说道,“准分子烧蚀瞬间将相容的目标材料(即聚合物、有机电介质)从固态转化为气态和副产物(即亚微米干碳颗粒),从而产生很少甚至没有热影响区以及更少的碎片。”

通过使用该技术,Suss一直专注于晶圆级工艺。此外,他还研发了双大马士革工艺RDL流程及其它技术。

“我们的产品路线图包括许多新项目。”Arendt说,“然而,最值得注意的两个问题是:(1)新的大视场、高NA投影物镜,可在生产中实现2μm的line/space;(2)双激光版本,可实现更大的扫描光束,从而显著提高产出量并降低购入成本。”

并且,Brewer Science公司正在研究另一种方法。它在注塑混合物中使用一种薄膜,就像模板一样工作,可解决芯片偏移问题。“这是环氧塑封材料的替代品。”Brewer高级技术执行总监Rama Puligadda说道,“你预先形成模板,然后可在那里用硅制造空腔。”

显然,用于封装的创新光刻解决方案并不缺乏。但是要突破1-1μm还需要继续努力。即使业内人士都知道这一点,但也必须满足客户苛刻的成本要求。这些因素都会让这个行业忙碌一段时间。

延伸阅读:

《iPhone X中A11处理器的台积电第二代InFO封装》

推荐培训:

《MEMS制造和封测培训课程》将于3月29日至31日在无锡举行,本课程邀请MEMS业内优秀讲师,重点剖析MEMS产业链的重要环节:(1)MEMS制造工艺;(2)典型MEMS器件工艺流程(如MEMS麦克风、压力传感器、非制冷红外探测器、MEMS微镜、喷墨打印头等);(3)MEMS封装技术;(4)MEMS测试技术(如加速度计、陀螺仪、磁传感器、压力传感器、MEMS麦克风等);(5)关键工艺设备和材料等,为大家展现MEMS产业的全貌和重要知识点。如果您有兴趣,请联系:

麦姆斯咨询

联系人:郭蕾

电话:13914101112

E-mail:Guolei@memsconsulting.com

上一篇:剪纸:从民间艺术到纳米制造

下一篇:罕王微电子8英寸MEMS芯片生产线建成投产