基于原位掺杂和浅台面型架构的短波红外InGaAs光电二极管

2023-12-10 20:27:05 来源:麦姆斯咨询 评论:0 点击:

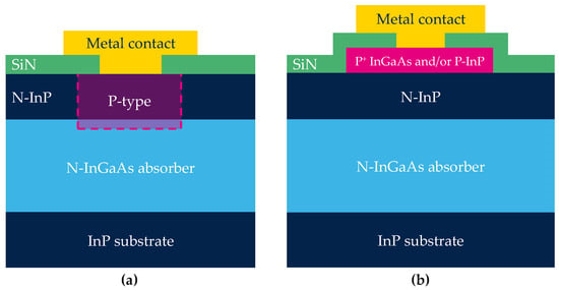

随着安防、汽车、工业、农业等各个领域需求的不断增长,短波红外(SWIR)传感器的发展也随之兴起。在1 ~ 2.5 μm的短波红外波段,硅材料是准透明的,因此,需要通过改变吸收材料来实现该波段光子的吸收。基于InGaAs的短波红外传感器的标准结构如图1a所示,该结构由一层外延生长于InP衬底上的厚膜低掺杂N-InGaAs吸收层组成。InGaAs图像传感器的制造目标是实现大尺寸、大规模的Si-CMOS兼容工艺。

图1 InGaAs光电二极管经不同制造工艺处理后的截面示意图

据麦姆斯咨询报道,由意法半导体(STMicroelectronics)、法国格勒诺布尔-阿尔卑斯大学(Univ. Grenoble Alpes,UGA)和法国国家科学研究中心(CNRS)组成的科研团队在Sensors期刊上发表了以“Design and Characterization of 5 μm Pitch InGaAs Photodiodes Using In Situ Doping and Shallow Mesa Architecture for SWIR Sensing”为主题的论文。该论文的第一作者为Jules Tillement,通讯作者为Jules Tillement和Frédéric Boeuf。

这项研究介绍了用于短波红外传感的浅台面型光电二极管的完整设计、制造和表征。对于InGaAs光电二极管的制造而言,关键工艺步骤是通过在N型堆叠中创建P区来定义每个像素。以往的研究报道了多种替代方案,包括Zn扩散、Be离子注入以及浅台面型架构。

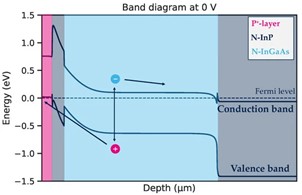

浅台面型架构设计的目的是在低反向偏压下从InGaAs吸收层收集光生载流子,以匹配读出集成电路(ROIC)的需求。少数载流子必须穿过如图2所示的模拟能带图上的异质结。N-InP层钝化了小间隙InGaAs层,但异质结为空穴收集引入了阻碍势垒。为了克服势垒,该结构被设计为通过引入一个电场来吸引处于平衡状态的载流子。

图2 模拟结构在平衡状态下的能带图

随后,研究人员利用Synopsys Sentaurus软件对该器件进行模拟,旨在寻找抑制收集路径静电壁垒的参数。这项理论研究使研究人员找到一组抑制空穴收集势垒的掺杂浓度和厚度参数。这组参数已被用于设定InGaAs光电二极管制造的外延堆叠。

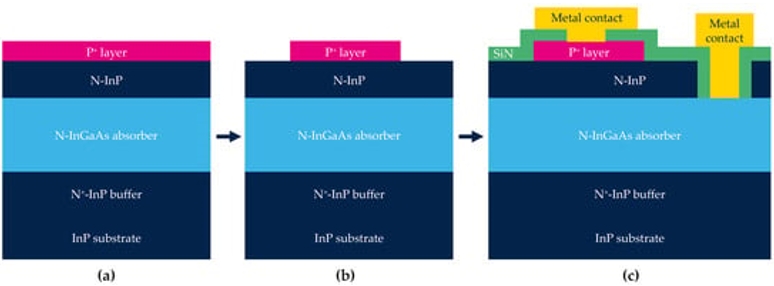

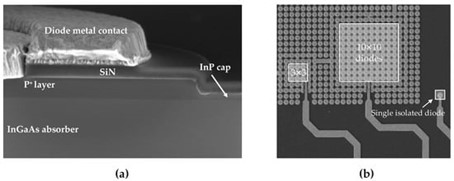

浅台面型光电二极管的原理图和简化工艺如图3所示。所有层均生长于3英寸InP衬底上(见图3a)。通过蚀刻P型层进行像素定义(见图3b和图4a)。然后,该器件通过介电沉积钝化。最后一步是制造二极管和N金属触点(见图3c)。

图3 浅台面型结构制造工艺流程的简化示意图

图4 完成制造工艺流程后的扫描电镜图(SEM)

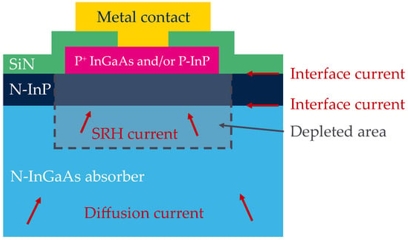

接着,研究人员首先在15 μm大像素上比较了两种工艺,以分析钝化对暗电流性能的影响。然后,采用最合适的工艺制备了5 μm像素间距的InGaAs光电二极管,并对其进行表征。最后,展示了3 μm像素间距的InGaAs光电二极管,作为像素间距缩减的案例。图5显示了该结构的横截面及其暗电流的潜在来源。

图5 该结构的横截面示意图及其暗电流的潜在来源

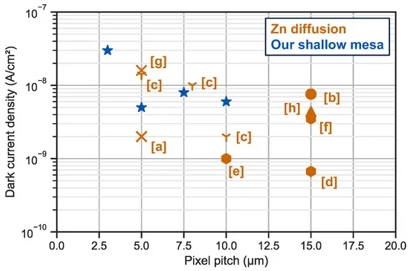

研究人员还使用既往研究中具有小间距和低暗电流的InGaAs光电二极管的最新数据与本研究的器件性能进行对比(参见图6)。与迄今为止报道的台面型架构相比,本研究提出的创新架构的性能有了重大改进。

图6 本研究在制造InGaAs光电二极管方面的成果(蓝色)与现有最新技术的比较

综上所述,凭借创新的浅台面型架构,这项研究设计并制备了性能优异的InGaAs光电二极管。在- 0.1 V和室温下,像素间距为5 μm时,该器件暗电流可低至5 nA/cm²。采用InP衬底和无抗反射涂层时,外部量子效率(QE)为54%。经过优化抗反射涂层和衬底去除工艺后,外部QE有望达到76%。对于低至3 μm的像素间距,该研究成功演示了InGaAs光电二极管的运行,虽然暗电流密度增加至30 nA/cm²。这种有前景的结构目前还在研究中,有望将其作为成像仪与Si-CMOS工具兼容的工艺以及Si-ROIC相集成。

论文链接:https://doi.org/10.3390/s23229219

延伸阅读:

上一篇:红外雪崩光电二极管(APD)的发展:从块体材料到二维材料

下一篇:最后一页