Tanner助力Instantaneous实现世界首款瞬时锁定环设计

2018-06-25 20:40:13 来源:麦姆斯咨询 评论:0 点击:

简介

Instantaneous Technologies是一家集成电路(IC)设计公司,他们凭借在模拟IC设计和物理版图领域数十年的丰富经验,克服了现有电路架构中众所周知的局限性,并依靠创新实现了性能的巨大突破。这些技术创新作为知识产权,以GDSII文件、网表、文档和一对一咨询的形式对外提供,以确保与现有项目的最佳整合。

Instantaneous Technologies公司首席技术官介绍说:“Tanner工具的灵活配置、灵敏的仿真和图形化界面,使我们能够利用这些技术实现快速设计、验证和记录我们的新型相位跟踪锁相环(PLL)。Tanner EDA中的S-Edit、T-Spice、Tanner Waveform Viewer和L-Edit的功能既方便易用,又全面合理,可帮助我们快速开发全新的电路架构。利用相同的工具,我们还可以轻松地迁移到新工艺节点上。然后通过先进的IP模块,Instantaneous Technologies为几乎所有的IC提供可量化的巨大优势。”

固有PLL限制

大多数IC设计人员都面临着PLL设计的挑战,并且需要学会处理:

• 典型PLL的稳定性问题。

• 大型环路滤波所需的大规模封装。

• 为了让具有毫秒级锁定时间的PLL收敛,即使他们有资源和时间来进行典型的全环路仿真,也需要至少一个星期的仿真时间,更不用说斜交角的仿真。

• 此外,权衡利弊带来的反复迭代也可能延长设计周期。

在一家知名半导体公司的大型工程团队中,关于一款销量上亿的微处理器PLL,流传着这样一个笑话,他们说从太空回望地球只能看到几样东西:中国的万里长城、澳大利亚的大堡礁,以及这种带有大型环路滤波器的微处理器PLL。当时,设计团队很反感这个笑话。在Tanner设计流程的帮助下,Instantaneous Technologies公司现在拥有了唯一一款“无法从太空看到的”PLL,它已完全不需要环路滤波电容器和维持PLL稳定性所需的超大电容器。该PLL实现了近乎瞬时的采集/锁定时间(8纳秒),比其他的快了数百万倍,并显示具有理想PLL的广泛跟踪带宽(数百MHz)。新的瞬时锁定环(ILL)同时改善了系统的价格和性能,让之前由于PLL限制而无法实现的新应用有望变为现实。尽管很多公司做出了大量的努力和无数的尝试,但在此之前,没有任何一家公司能够完成这项工作。

理想的PLL

利用新型革命性的相位跟踪、超相位协调(UPC),可在新的ILL中实现PLL性能的巨大飞跃。它的其中一个优点便是开发时间只有典型PLL的几分之一。使用T-Spice,ILL仿真从启动到锁定可能只需要不到半小时,而典型的PLL则要一周之多。由于实现锁定所需的运行时间过长,典型的PLL通常不能作为全环路进行仿真。Tanner工具和T-Spice数值方法的易用性,有助于改善这一点,但这种仿真加速主要取决于快速的ILL采集时间。Tanner Waverform Viewer可以轻松地在一组有用的频率特征图中显示仿真结果,包括在其他仿真环境中无法提供的频率/时间图。与典型PLL相比,ILL设计的其他优点包括:

• 大幅缩短设计和仿真时间。

• 8纳秒采集/锁定时间,功耗节省与系统尺寸成正比。

• 消除抖动峰值和抖动累积,使得相位噪声降低100倍。

• 1/50的芯片面积,使成本微乎其微。

• 理想的相位跟踪,可通过低相位噪声或基准调制。

• 迅速迁移到新的工艺节点。

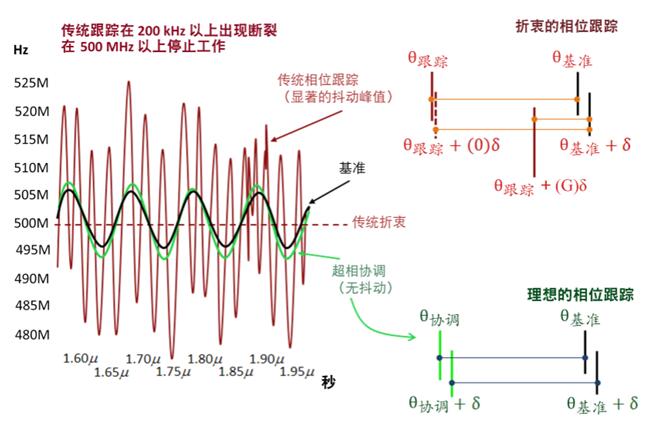

图1显示了理想的ILL相位协调与传统相位跟踪方法的比对。随着ILL环路增益的增加,可在消除抖动峰值的同时实现理想的相位跟踪和超相位协调。在基准相位上任何频率处的任何偏移δ都会在跟踪相位上分毫不差地完全复制。随着环路增益G的增加以改善典型PLL中的相位跟踪,环路会相应地变得不稳定,从而导致抖动峰值。为避免这种不稳定性,典型的PLL中通常使用大型环路滤波电容器来使环路保持极低的增益。保持低环路增益后,基本上不能跟踪基准相位,并且环路需要数秒或数毫秒后才能收敛。如此一来,PLL更容易出现由于环路的器件噪声或电源噪声引起整个环路的抖动累积和不可预测的抖动。在频率合成的情况下,来自晶体的基准相位的低相位噪声被环路滤波器阻挡,从而将来自抖动累积和压控振荡器的更高的相位噪声施加在输出时钟上。

图1:UPC,理想的相位跟踪

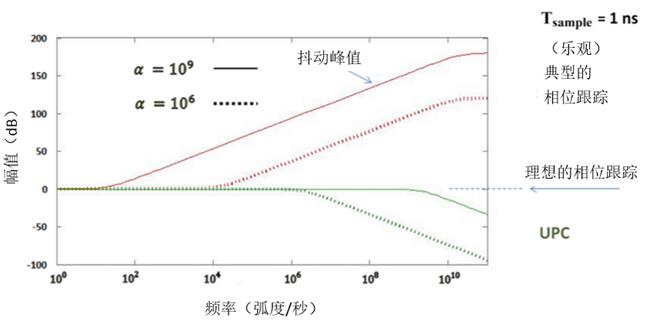

抖动传递函数(JTF)图更简洁地描述了ILL的优点(图2)。随着环路增益α的增加,UPC相位跟踪随之增强,这与传统方法中的相位跟踪减弱恰恰相反。因此,ILL消除了跟踪带宽与环路稳定性之间的权衡,以及围绕这一权衡展开优化所需的多重设计迭代。这将大幅缩短设计周期。

图2:随着环路增益的增加,UPC可以改善跟踪,这与典型的PLL恰恰相反

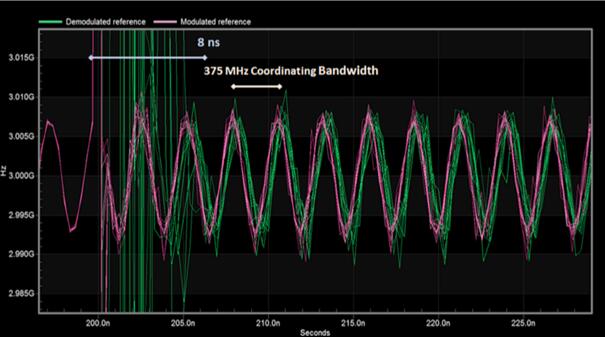

图3显示了在Tanner Waveform Viewer中提供的非常有用的直接频率图中ILL的协调带宽。特别是直接频率/时间图,大大简化了ILL的开发。

图3:ILL的采集时间和协调带宽显示了多个数量级的改善

在军用规格和3-σ偏移材料要求的温度范围内执行55纳米ILL锁定环的仿真,以验证其鲁棒性,显示收敛时间在8纳秒以内,其速度之快是典型PLL的数百万倍。即使这些完整的环路仿真在高毫秒的第二次收敛时间内以低纳秒时间间隔禁止运行时间来执行,正常的PLL仿真时间也需要数周才能锁定。不难看出协调(跟踪)带宽的频率是375MHz,是典型PLL的2500倍。这可能是由于UPC所致。跟踪带宽随基准频率而变化,该频率在集成度更高的工艺节点中可能超过1GHz。

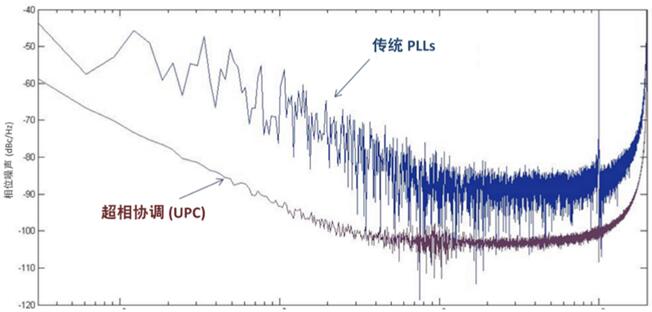

对于ILL和典型的PLL,除单独的相位检测外,相位噪声(图4)均从相同的非优化环路进行测量。集成到Tanner Waveform Viewer中的快速傅里叶变换(FFT)可通过将数据量减少几个数量级以便轻松提取数据用于进一步的处理,来加速生成相位噪声图。ILL的相位噪声只有典型PLL的百分之一,因此设计人员能够增加时钟分配的时间余量,或提高时钟频率。

图4:ILL降低了相位噪声

频率混叠是PLL设计中常见的问题之一,然而ILL从设计上消除了这一问题。此外,相关的谐波失真可能成为某些PLL应用的障碍,因为一次和二次谐波通常高达基准信号功率的1/10。ILL从设计上消除了谐波。

IP可迁移性

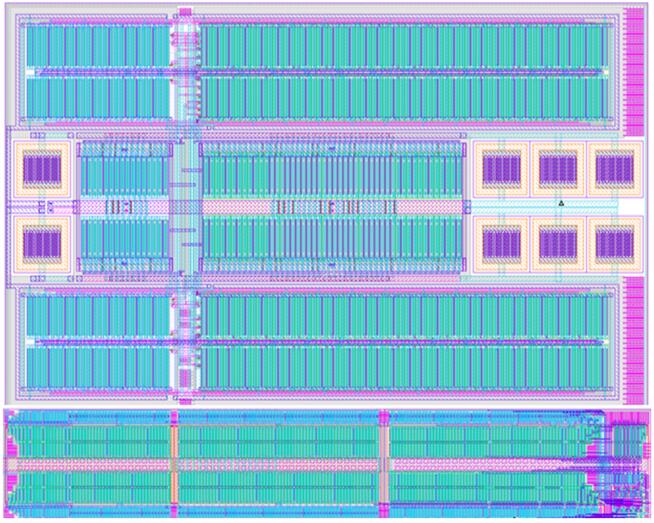

显然,在L-Edit图中55纳米ILL的版图布局中没有典型的大型环路滤波器(图5)。实践证明L-Edit以及用于电路设计和仿真的工具非常有针对性,恰好提供了快速完成任务所需的一切。明显缩小的版图尺寸(在平方微米范围内)也有助于可迁移性和可用性。例如,小尺寸可确保高频信号不需要通过长布线进入ILL。物理版图中的器件匹配和布线选择要求相对不那么严格,这意味着可借助L-Edit简单易用的功能大幅加快在新工艺节点(可迁移性)的速度。

图5:ILL物理版图

如180和55纳米工艺所示,由于ILL的采集时间只需8纳秒,使用T-Spice和Tanner Waveform Viewer能够以十万倍的速度进行全环路仿真。与目前使用的PLL所能实现的方案相比,ILL具有数百万倍的运行速度,因而能通过更多稳健的斜交角进行更为全面的功能验证。由于采集速度快,ILL也可以同时用整个时钟分布和系统模块进行仿真,从而更全面地查看接口和性能。此外,考虑到环路稳定性会高得多,对物理版图细节的关注和所花费的时间要少于传统PLL。凭借ILL独有的这两项主要特性,还可以将IP快速迁移到任何目标工艺节点上,从而降低生产成本。低成本加上理想的相位跟踪和后续的性能优势,使ILL成为目前广泛应用的传统PLL的理想替代品,它几乎可定义所有集成电路都在使用的时钟,包括无线电、电信和计算机等。

数学匹配

在硅芯片上使用示波器JTF测量显示在200kHz下有0.02%的抖动,但具有讽刺意味的是,现有的测试设备只能测量到200kHz,远不及ILL所能达到的600MHz(ILL要快3000倍)。测试设备制造商没有预料到ILL的出现。其他测量结果表明,硅芯片和建模之间存在良好的匹配。

总体测试结果证实,用于时钟应用的最佳抖动控制措施是具有高增益的环路,它能最准确地跟踪来自晶体的最细小的抖动。既然设计人员打算使用昂贵且更容易受电源和环路中的CMOS器件噪声影响的大型环路滤波器来限制低相位噪声(抵消晶体的关键优势),为什么还要使用相对较贵且具有低相位噪声的晶体呢?使用ILL是一种更为简洁的解决方案,该解决方案可以跟踪晶体的低相位噪声,消除环路滤波器中的大型电容器,进而定义更严格的时钟。在需要跟踪基准信号调制的其他应用中,ILL是唯一的解决方案。加之1/50甚至更小的芯片面积,大幅缩短的开发时间,以及8纳秒的采集时间(可节省启动时功耗),让ILL成为理想化的PLL,ILL是适合各种PLL应用的卓越解决方案。

麦姆斯咨询和Mentor建立战略合作伙伴关系,麦姆斯咨询代理销售Tanner系列EDA软件,并开展专题研讨会及培训课程。

联系方式:

麦姆斯咨询

联系人:王懿

电话:17898818163

电子邮箱:WangYi@MEMSConsulting.com