Verilog-A将设计精度推向新高度

2018-07-11 10:48:07 来源:麦姆斯咨询 评论:0 点击:

简介

使用Verilog-A可以提高设计人员的生产效率和准确性。您可以通过Verilog-A提高仿真性能,从而:

- 以更快的运行时间完成行为建模,并在早期运行系统级仿真。

- 进行特殊检查和测量,例如安全工作区的检查。

- 创建复杂的输入激励。

- 创建非标准器件的模型,例如微机电系统(MEMS)、图像传感器或薄膜晶体管(TFT)。

Verilog-A的优点

- 在设计周期的早期运行系统级仿真,从而找出系统集成问题,尽量避免在设计周期的后期进行重新设计。

- 执行特殊测量,例如:微分非线性(DNL)、积分非线性(INL)和相对建立时间。

- 在仿真期间运行安全工作区检查,包括电压是否处于规定范围或器件是否在指定区域内运行。

- 混合并匹配模块在行为和器件级的模型,以加快运行时间。

- 轻松创建复杂的输入激励,例如随机信号、伪随机比特流、限幅信号、非线性压缩或采样信号。

- 使用简单有效的器件行为描述语言,针对TFT、图像传感器、太阳能电池、晶体管或MEMS等特殊器件创建自己的模型。

行为建模

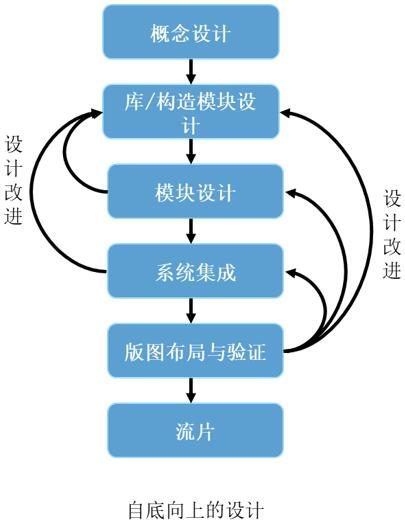

模拟设计通常采用的是自底向上的设计方法。这个方法的缺陷是,如果在设计周期的后期发现系统集成问题,可能会造成额外的费用支出和工作投入。

图1:传统的自底向上的模拟设计方法可能会造成额外的费用支出和工作投入

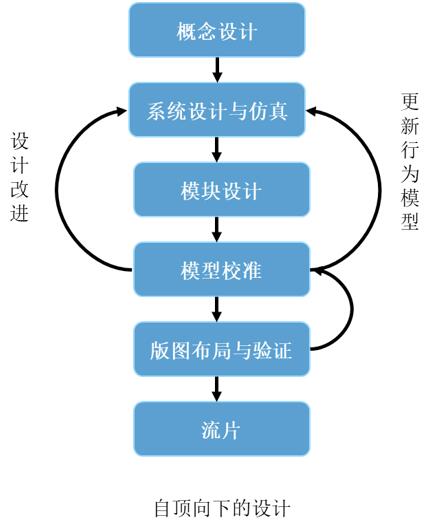

Verilog-A可以实现自顶向下的电路设计,鼓励设计人员在早期运行系统级仿真,以验证接口和系统集成问题。设计人员为各个主要的设计模块创建行为模型,然后开始执行系统级仿真,从而确保可以准确连接所有设计模块。完成系统级的设计之后,设计人员可以进行器件级的单个模块的设计,然后在详细设计时对各个模块的行为模型进行校准。经过校准的行为模型可用作下一个设计的系统级仿真的初始模型。

图2:Verilog-A可以实现自顶向下的设计,有助于在早期验证接口和系统集成问题

使用Verilog-A创建行为模型的另一大优点,是它可以实现行为模块与器件级模拟网表之间的协同仿真,从而加快仿真速度、缩短设计周期。

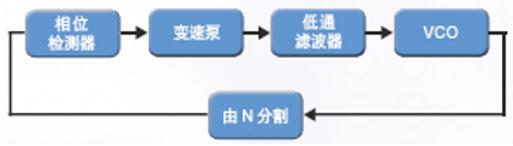

设计锁相环路(PLL)时,您可以混合并匹配模块在行为和器件级的模型,达到所需的仿真精度和运行时间之间的平衡。

图3:PLL框图

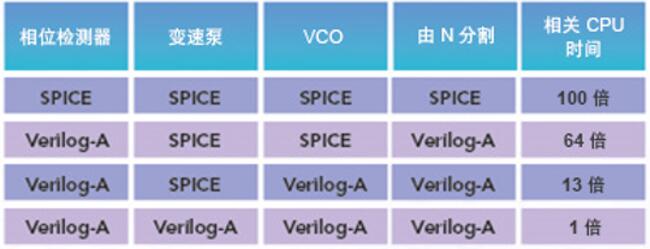

下面是PLL仿真运行时间表,其中各个模块都具有行为和器件级的模型。仿真运行时间是通过结合不同的模块表示进行测量的。这样,设计人员在关注模块级设计的同时,还能快速执行系统级仿真。

图4:PLL仿真运行时间

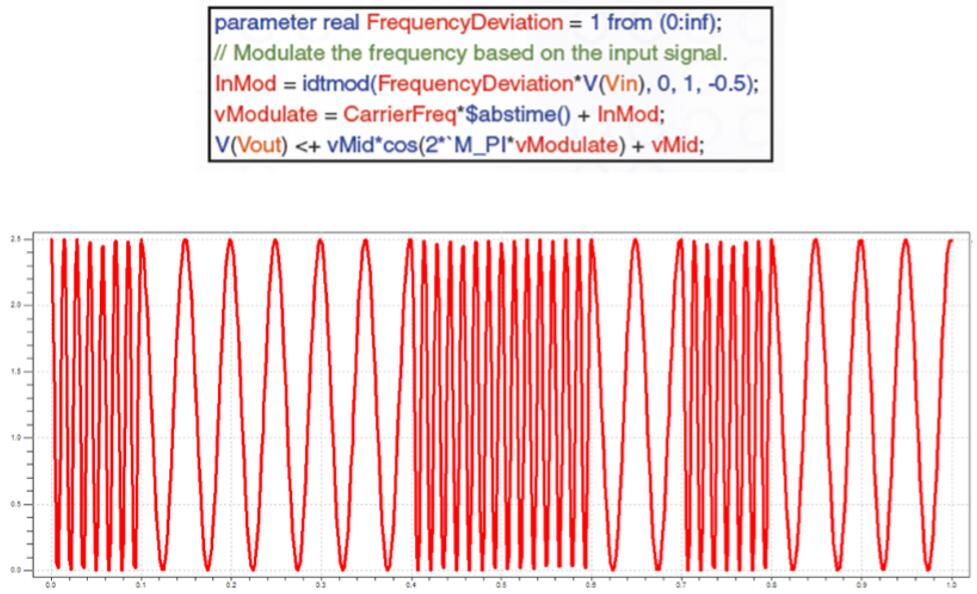

设计人员可以使用数学方程式或传递函数快速创建复杂的行为模型,甚至只需三行代码就能创建出调频(FM)调制器。

图5:Verilog-A FM调制码、FM数字信号调制

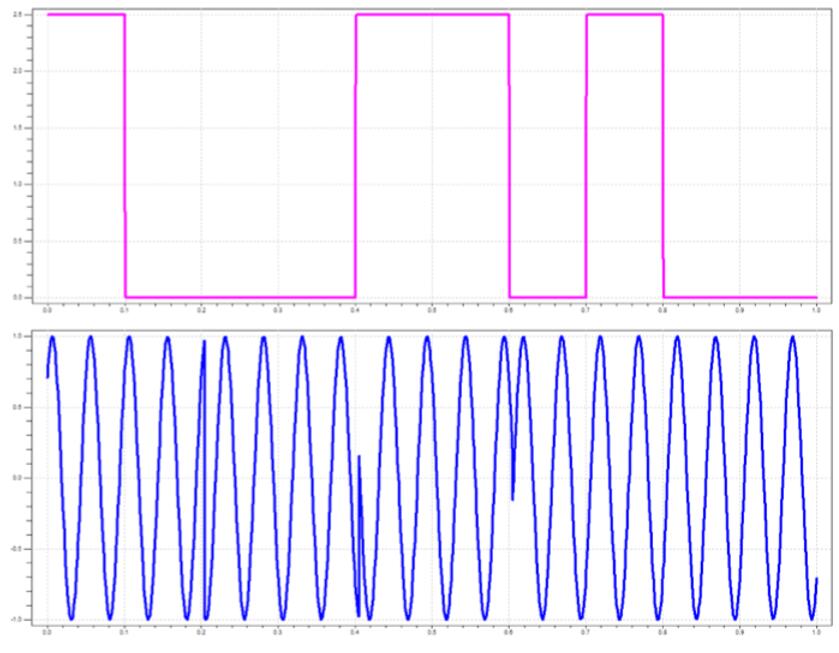

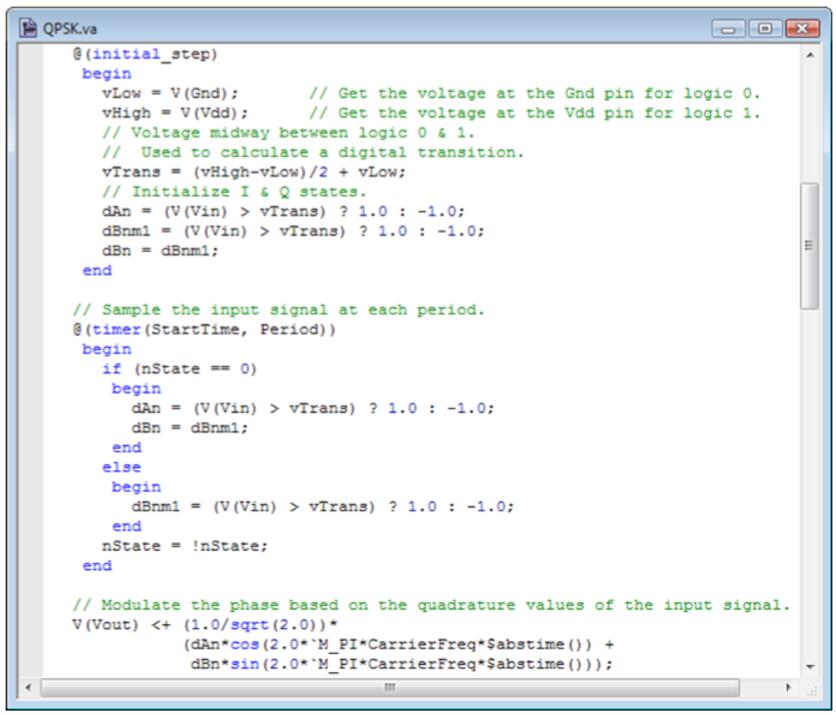

Verilog-A尤其有助于混合信号模块的建模。设计人员可以通过10行代码构建正交相移键控(QPSK)调制器,而且比全SPICE表示运行速度快了20倍以上。

图6:QPSK数字信号调制与Verilog-A QPSK调制码

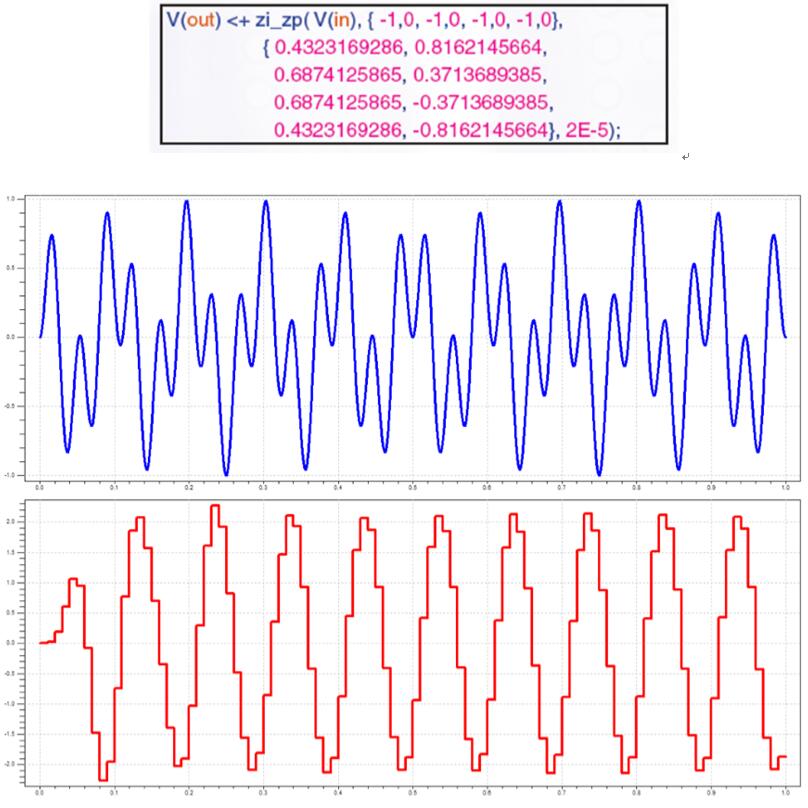

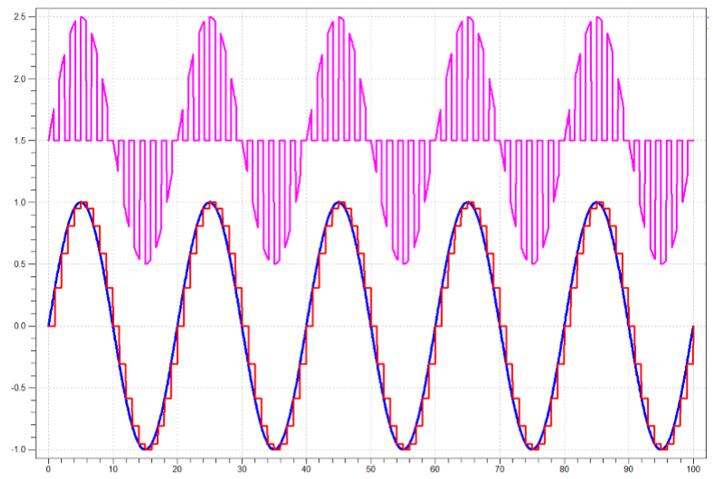

您可以使用Verilog-A中的laplace_xx和zi_xx函数在s域和z域中轻松指定传递函数,并且只需1行代码就能描述四阶低通3dB纹波切比雪夫滤波器。

图7:Verilog-A针对四阶低通3dB纹波切比雪夫滤波器的代码、输入信号和输出信号

安全工作区

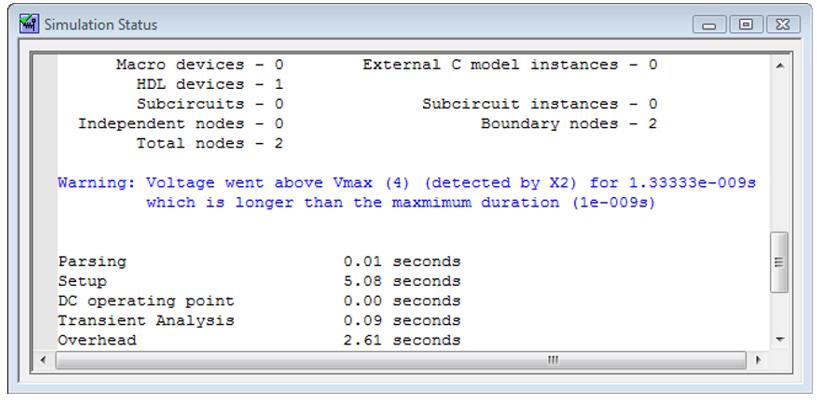

Verilog-A还可以不断扩展设计人员的设计需求,使他们能够在设计周期的早期发现设计错误。您可以通过Verilog-A执行特殊检查,例如安全工作区(SOA)的检查。您可以监控仿真期间的电压,并在节点或管脚电压超出安全工作范围时发出警报。这样有助于确保模数转换器(ADC)的输入电压始终保持在其可承受的电压范围内。甚至您还可以检查在超过特定时段后电压是否高出指定电压。

监控电压可以帮助您确保栅极到源极的电压始终稳定在使模型有效的电压范围内。

图8:超过规定范围的电压的仿真结果

设计人员还可以设置针对特定金属氧化物半导体场效应管(MOSFET)的工作范围。如果这些器件没有在指定区域内运行,例如线性或饱和区域,设计人员可以使用Verilog-A发出警报。通过Verilog-A创建的简化模型可以被修改为在任何范围内的SOA检查。

特殊测量

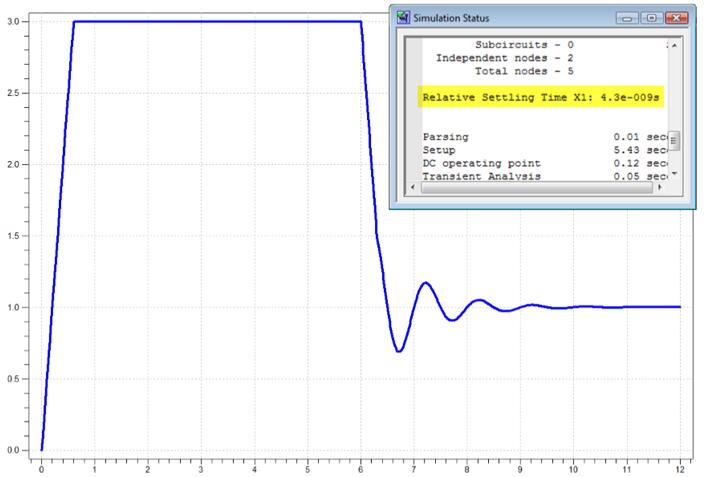

设计人员通常需要执行一些无法通过SPICE的测量(Measure)命令实现的复杂测量。通过Verilog-A,您可以测量非常复杂的电路特性,包括模数转换器(ADC)和数模转换器(DAC)的微分/积分非线性(DNL/INL)、相关建立时间(如不清楚最终稳态值),以及PLL抖动测量值。

复杂的输入激励

图9:相关建立时间的测量结果

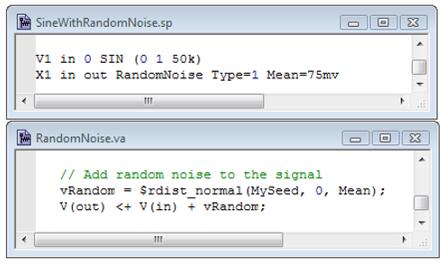

您可以轻松创建无法通过SPICE实现的输入激励。您可以在电路中添加随机信号,然后检查设计对噪声的反应情况。

图10:为信号添加随机噪声的SPICE平台与Verilog-A代码

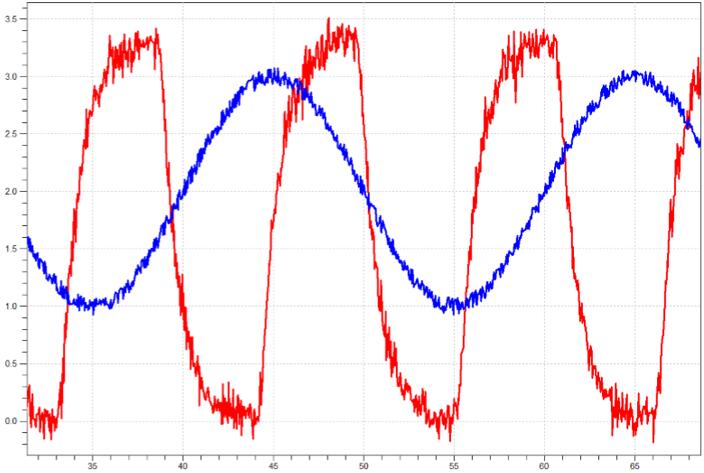

图11:带随机噪声的信号

您可以创建伪随机比特流、限幅信号或非线性压缩信号。您还可以基于不同的采样率或方案创建采样数据。

图12:主信号与使用Verilog-A的不同采样结果

模型开发

如果您需要为TFT、太阳能电池、晶体管、横向扩散金属氧化物半导体(LDMOS)、图像传感器或MEMS等特殊器件创建自己的模型,Verilog-A可以为您提供有效描述器件行为的语言。EKV3.0、BSIM3.3和BSIM3.4等众多标准模型已经有Verilog-A格式。您可以修改和扩展现有模型,例如二极管模型,以包含静电放电(ESD)和折回效应(snapback effect)。

有些晶圆代工厂很快将提供针对非标准器件的Verilog-A模型,与使用SPICE内置器件组合的子电路相比,这些非标准器件无法达到同样的仿真水平。Verilog-A提供了用于器件行为建模的标准高级语言,适用于各种仿真器。

麦姆斯咨询和Mentor建立战略合作伙伴关系,麦姆斯咨询代理销售Tanner系列EDA软件,并开展专题研讨会及培训课程。

联系方式:

麦姆斯咨询

联系人:王懿

电话:17898818163

电子邮箱:WangYi@MEMSConsulting.com